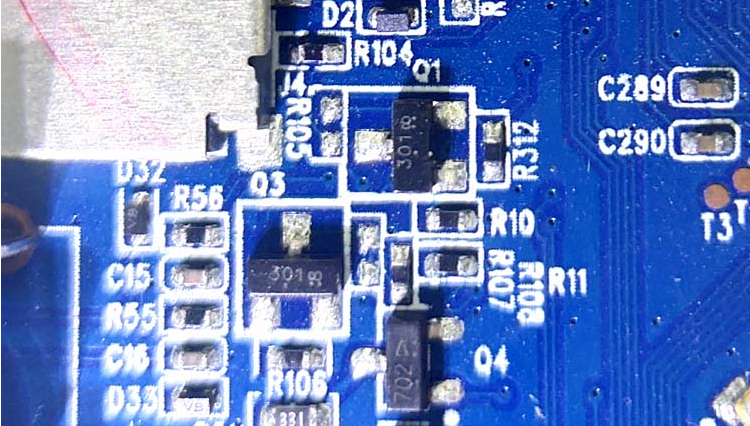

The FDV301N N-channel logic level enhancement mode field effect transistor is produced using Fairchild Semiconductor's proprietary high cell density DMOS technology. This device is located on the Whatsminer H3 control board and is designed to minimize on-resistance. Since no bias resistors are required, this N-channel FET can replace several digital transistors with different bias resistor values.

Features:

• 25 V, 0.22 A continuous, 0.5 A Peak. RDS(ON) = 5 Ω @ VGS= 2.7 V RDS(ON) = 4 Ω @ VGS= 4.5 V.

• Very low-level gate drive requirements allowing direct

• operation in 3V circuits. VGS(th) < 1.5V.

• Gate-Source Zener for ESD ruggedness. >6kV Human Body Model

• Replace multiple NPN digital transistors with one DMOS FET.

70901.9USD

70901.9USD 56.42USD

56.42USD 1.42USD

1.42USD 0.1USD

0.1USD 2165.47USD

2165.47USD 8.68USD

8.68USD 643.57USD

643.57USD 91.86USD

91.86USD 0.06USD

0.06USD 0.04USD

0.04USD 0.06USD

0.06USD

Favorites

Favorites History

History

Feedback

Feedback